Skip to content

- UART

- MARK (Logic 1) = Logic High

- Space (Logic 0) = Logic Low

- Idle Line = Logic High

- Line-break/open line = Continuous Logic Low

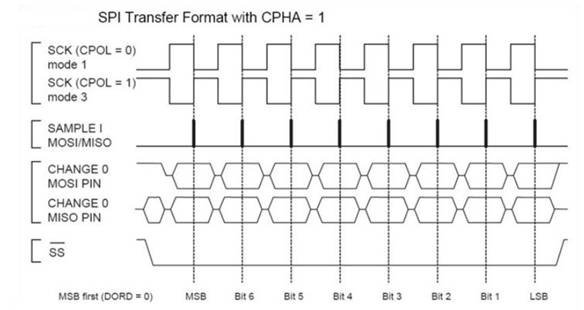

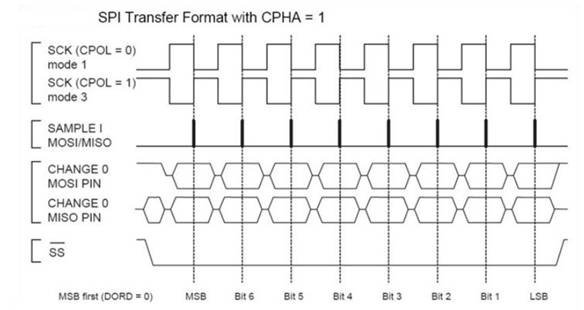

- SPI

- Slave Mode

- Idle Pattern: A7B4

- Maximum Clock = 6.8 MHz

- Default Clock Polarity and Phase: CPOL = 0, CPHA = 1

- Timing

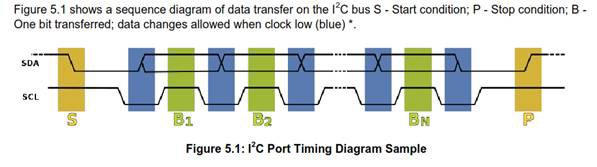

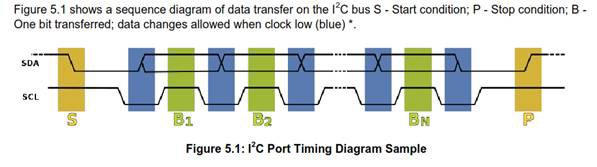

- I2C

- Default Address Format: 7-bit

- Master Address (sending) is 0x62

- Slave Address (receiving) is 0x60

- Data Frame Size: 8-bit octets

- Data Bit Order: MSB,LSB

- Data Rates: Default = Fast Mode (400 kbps), Standard Mode (100kbps)

- Timing

Posted in: GPS, Sirf IV

Inventek

2012-08-16T15:41:06-04:00 2018-06-27T03:34:32-04:00